SHAPES project

INFN Roma group in the SHAPES project

The INFN Roma group's contribution to the SHAPES project consist of a TLM-SystemC and a VHDL model of the DNP.

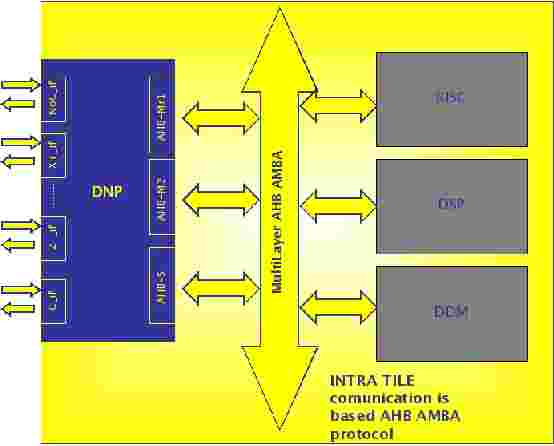

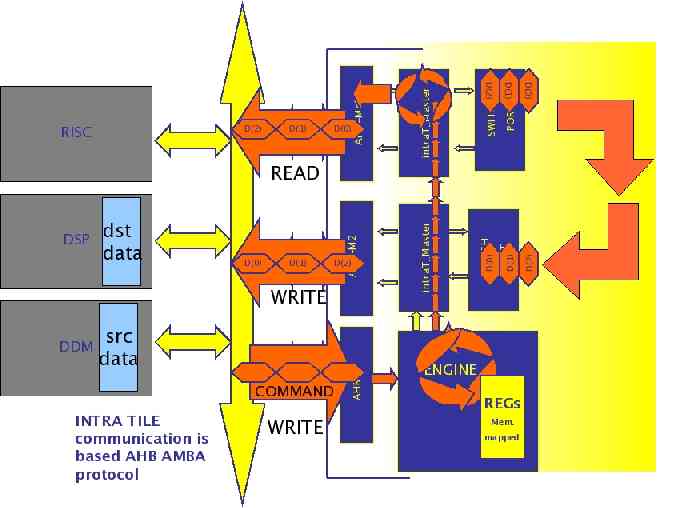

DNP stands for Distributed Network Processor. The main task of the DNP is to provide inter-tile communication services. A secondary service is to act as a DMA controller for intra-tile communications. The DNP offers its services to other masters in the tile, typically a RISC or a DSP processor.

The picture below shows the DNP in the RISC-DSP Tile (RDT).

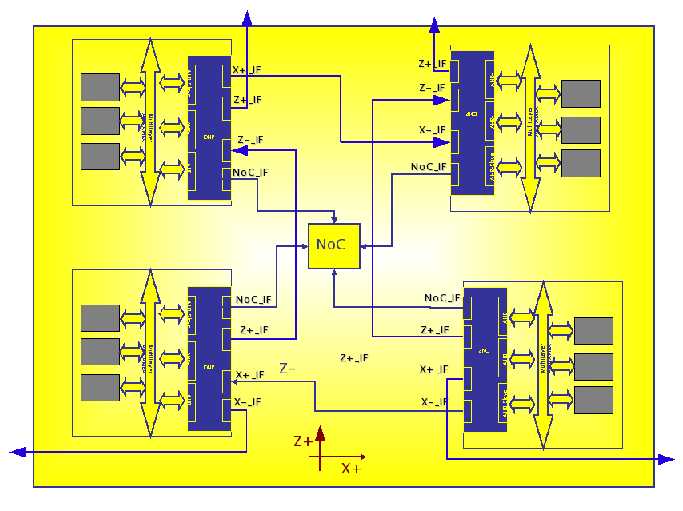

The SHAPES architecture is a scalable architecture, based on tiles. The scalability is assured by the DNP which provide a set of inter tile communication port for on-chip and off-chip communications. The on-chip communications between tiles is guaranteed by the Spidergon NoC, while the off-chip links are based on a serial protocol to support 3D lattice architectures.

An example of SHAPES chip and SHAPES lattice, is showed below:

The Distributed Network Processor

This section contains a brief description of the DNP and its role in the SHAPES tile