Difference between revisions of "SHAPES project"

| (3 intermediate revisions by the same user not shown) | |||

| Line 22: | Line 22: | ||

[[Image:DNPintheCHIP_small.jpg]] | [[Image:DNPintheCHIP_small.jpg]] | ||

| − | The pictures show as the DNP is the communication engine in the shapes tile. It support the communication inside the tile via two masters ans one slave AHB AMBA ports, and outside the tile with a NoC port and six links for 3D connections. The DNP is designed to support another link for the collective. The collective link | + | The pictures show as the DNP is the communication engine in the shapes tile. It support the communication inside the tile via two masters ans one slave AHB AMBA ports, and outside the tile with a NoC port and six links for 3D connections. The DNP is designed to support another link for the collective. The collective link allows direct connections between nodes not connected by the 3D lattice. |

==== The SHAPES tile in a 3D lattice ==== | ==== The SHAPES tile in a 3D lattice ==== | ||

| Line 28: | Line 28: | ||

[[Image:SHAPES3Dlattice_ex.jpg]] | [[Image:SHAPES3Dlattice_ex.jpg]] | ||

| − | [[DNP inner | + | === The Distributed Network Processor: HW architecture === |

| + | |||

| + | The DNP receives commands issued on a slave port by the initiating processors (the RISC or the DSP). One command is done by 8 words. | ||

| + | |||

| + | [[Image:command.jpg]] | ||

| + | |||

| + | The DNP is also equipped with two master ports to sustain the data traffic on the AMBA Multilayer bus. In a typical situation those master ports act simultaneously to sustain the flow between the source and the destination device (memory buffers exposed to the DNP by the tile: i.e. DXM, DDM, DPM, RDM, RPM, POT). | ||

| + | For intra-tile communications, the set of master and slave interface ports would suffice. For inter-tile communication, which require the cooperation of at least two DNPs located on different tiles, the DNP is equipped with a set of inter-tile interfaces. A first set of those interfaces are used for off-chip communications on a 3D toroidal next-neighbors topology and on a collective communication tree. A second set of interfaces will be used for on-chip communication through a dedicated NoC architecture. | ||

| + | The DNP's brain are the inner blocks called ENGINE, ARBITER and ROUTER. | ||

| + | |||

| + | [[Image:dnp_HW_spec_v1_small.jpg]] | ||

| + | |||

| + | The data inside the DNP and in the whole set of the inter tile ports travels as packet. | ||

| + | The ENGINE's main task is to interpret the commands coming from the intra tile bus (AMBA AHB in this version) via the AHB TLM Slave port. Other ENGINE's task is to support the intra tile master blocks in building the packets once the command has been already decoded (see next chapters for more details). | ||

| + | |||

| + | [[Image:packet.jpg]] | ||

| + | |||

| + | The ARBITER and the ROUTER, applying a priority scheme and a fixed routing algorithm, take care to drive the packets from one DNP port to another DNP port. | ||

Latest revision as of 15:31, 20 September 2007

INFN Roma group in the SHAPES project

The INFN Roma group's contribution to the SHAPES project consist of a TLM-SystemC and a VHDL model of the DNP.

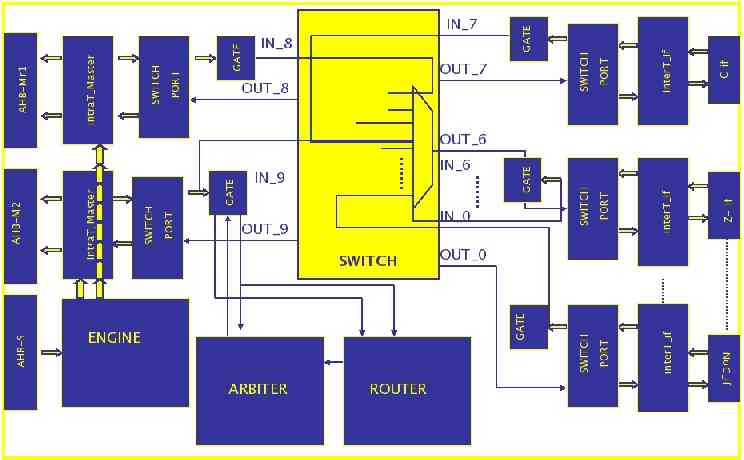

The Distributed Network Processor in the SHAPES Tile

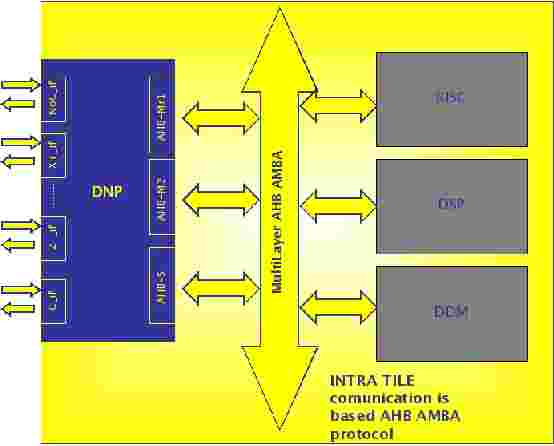

DNP stands for Distributed Network Processor. The main task of the DNP is to provide inter-tile communication services. A secondary service is to act as a DMA controller for intra-tile communications. The DNP offers its services to other masters in the tile, typically a RISC or a DSP processor.

The picture below shows the DNP in the RISC-DSP Tile (RDT).

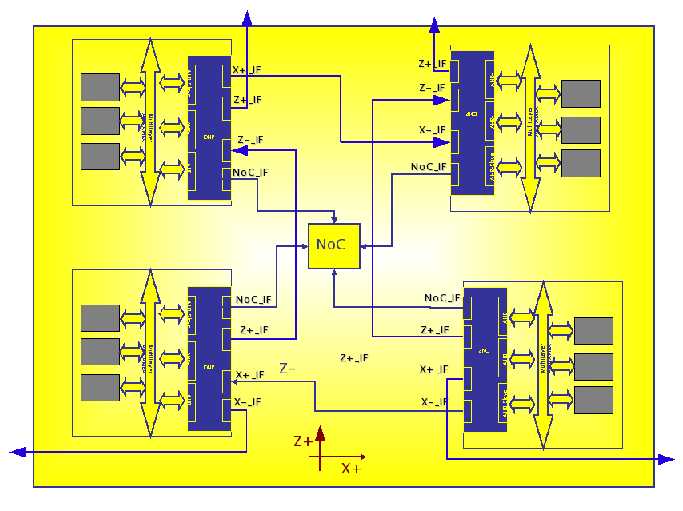

A scalable architecture: the DNP and the interTile communication ports

The SHAPES architecture is a scalable architecture, based on tiles. The scalability is assured by the DNP which provide a set of inter tile communication port for on-chip and off-chip communications. The on-chip communications between tiles is guaranteed by the Spidergon NoC, while the off-chip links are based on a serial protocol to support 3D lattice architectures.

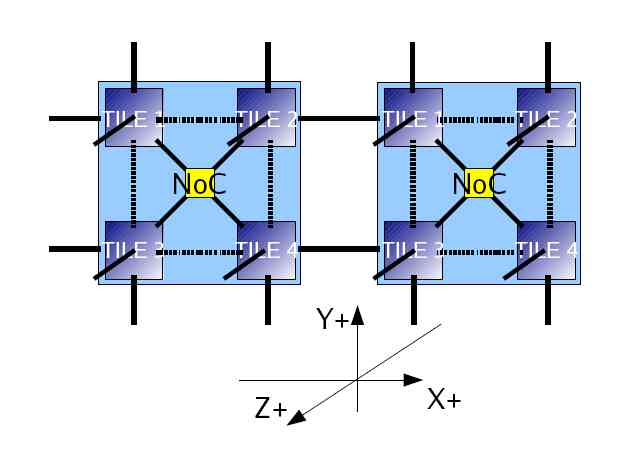

One chip, multiple tiles

An example of SHAPES chip, is showed below:

The pictures show as the DNP is the communication engine in the shapes tile. It support the communication inside the tile via two masters ans one slave AHB AMBA ports, and outside the tile with a NoC port and six links for 3D connections. The DNP is designed to support another link for the collective. The collective link allows direct connections between nodes not connected by the 3D lattice.

The SHAPES tile in a 3D lattice

The Distributed Network Processor: HW architecture

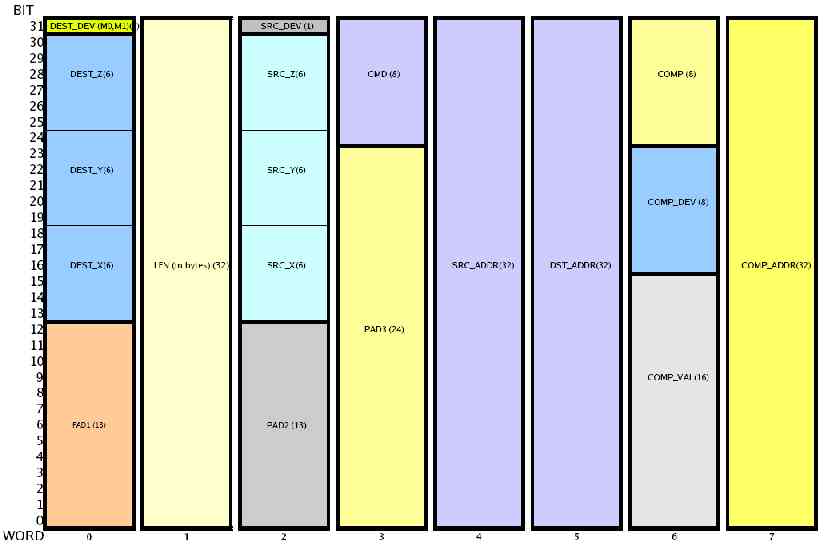

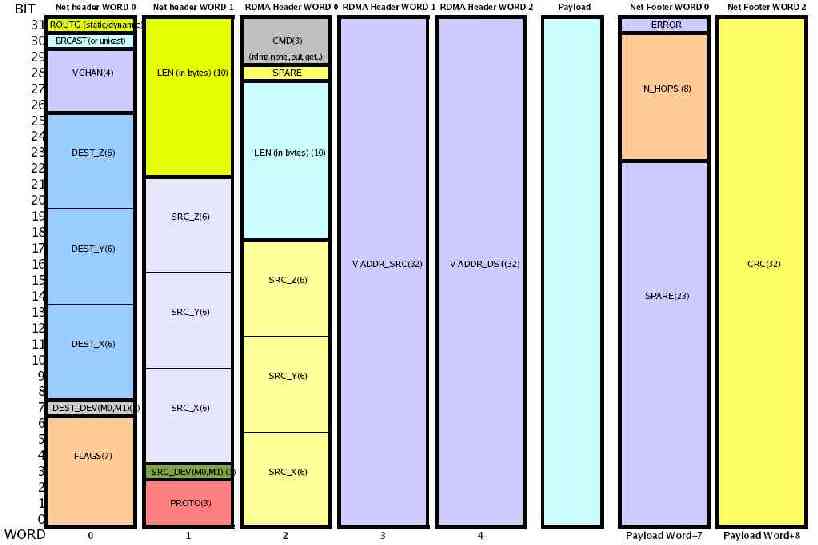

The DNP receives commands issued on a slave port by the initiating processors (the RISC or the DSP). One command is done by 8 words.

The DNP is also equipped with two master ports to sustain the data traffic on the AMBA Multilayer bus. In a typical situation those master ports act simultaneously to sustain the flow between the source and the destination device (memory buffers exposed to the DNP by the tile: i.e. DXM, DDM, DPM, RDM, RPM, POT). For intra-tile communications, the set of master and slave interface ports would suffice. For inter-tile communication, which require the cooperation of at least two DNPs located on different tiles, the DNP is equipped with a set of inter-tile interfaces. A first set of those interfaces are used for off-chip communications on a 3D toroidal next-neighbors topology and on a collective communication tree. A second set of interfaces will be used for on-chip communication through a dedicated NoC architecture. The DNP's brain are the inner blocks called ENGINE, ARBITER and ROUTER.

The data inside the DNP and in the whole set of the inter tile ports travels as packet. The ENGINE's main task is to interpret the commands coming from the intra tile bus (AMBA AHB in this version) via the AHB TLM Slave port. Other ENGINE's task is to support the intra tile master blocks in building the packets once the command has been already decoded (see next chapters for more details).

The ARBITER and the ROUTER, applying a priority scheme and a fixed routing algorithm, take care to drive the packets from one DNP port to another DNP port.