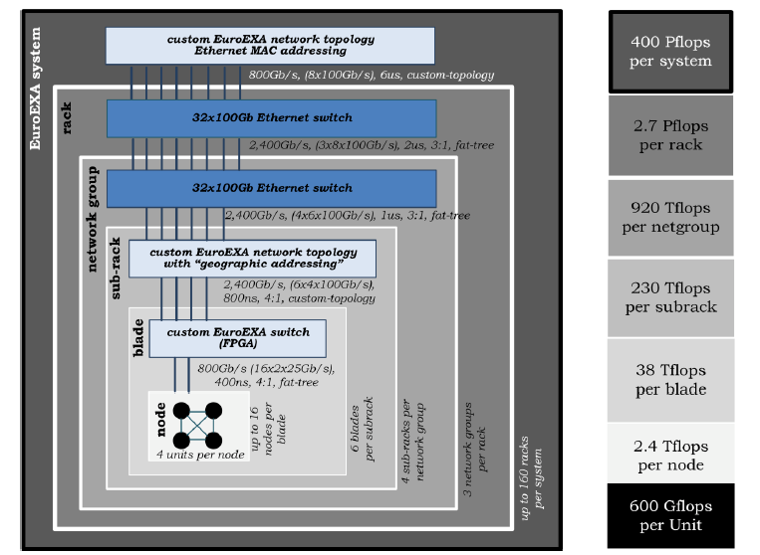

EuroEXA, funded by the European Union, started in September 2017 aiming to design a balanced architecture for both compute- and data-intensive applications using a cost-efficient, modular-integration approach enabled by novel inter-die links and the tape-out of a resulting EuroEXA processing unit with integration of FPGA for data-flow acceleration. EuroEXA will provide a homogenised software platform offering heterogeneous acceleration with scalable shared memory access and create a unique hybrid geographically-addressed, switching and topology interconnect within the rack while enabling the adoption of low-cost Ethernet switches offering low-Latency and high-switching bandwidth.

System Architecture and Technology

- ARM processing and FPGA DataFlow

- Unimem Architecture with PGAS

- Distributed Storage on BeeGFS

- Memory Compression Technologies

- Hybrid Geographically-Addressed Switching and Topology Interconnect

Path towards Exascale

- Testbed 1 provides 50 nodes of new technology for software development.

- Testbed 2 provides 500 nodes and new infrastructure technologies to test scaling

- Testbed 3 tests new node and processor technologies that will ultimately project to Exascale

The APE lab activities will focus on the design of Blade Level Custom EuroEXA Switch component, contributing to the design, debug and optimisation of:

- the switch and its links to the computing nodes;

- the novel routing functions for packet routing at blade level;

- the packet aggregation and routing mechanisms for intra-blade connectivity at sub-rack level.